Monday, May 22, 2024

Signal Integrity in HDI Design: What Causes Failures First

by

Published

Views:

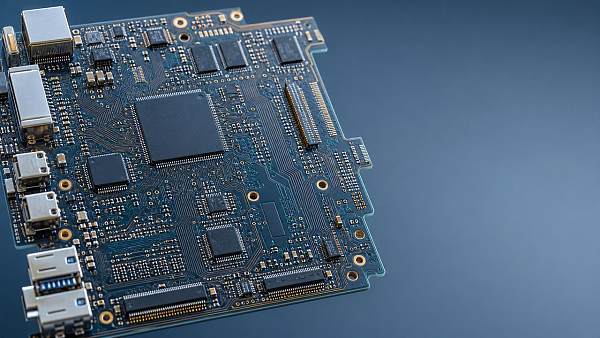

Signal integrity in HDI design often fails long before visible defects appear—through impedance discontinuities, crosstalk, via stubs, and stack-up mismatches that quietly erode performance. For technical evaluators comparing advanced interconnect platforms, understanding what breaks first is essential to reducing risk, validating compliance, and ensuring reliable high-speed transmission in increasingly dense electronic architectures.

Why does signal integrity in HDI design fail before anything looks wrong?

In high-density interconnect environments, failure rarely begins with a burned trace or an obvious open circuit. It usually starts as a margin loss problem. A channel still functions in the lab, but eye height narrows, timing jitter rises, insertion loss accumulates, and electromagnetic coupling increases. By the time a board shows unstable communication in the field, the first signal integrity weakness may have been present from the stack-up review stage.

For technical evaluators, this matters because HDI substrates are now used across electronics, automotive control systems, industrial sensing, smart agriculture platforms, and environmental infrastructure. A design choice that seems acceptable in one product class may fail under the thermal, vibration, or compliance demands of another. Signal integrity in HDI design is therefore not just a layout issue; it is a cross-functional risk issue tied to procurement, validation, and lifecycle reliability.

Global Industrial Matrix approaches this challenge from a benchmarking perspective. Rather than treating HDI design as an isolated PCB topic, GIM evaluates how substrate geometry, material selection, via architecture, process consistency, and standards alignment affect system-level performance across sectors. This is especially useful when procurement teams and engineering teams must compare suppliers that present similar datasheets but very different manufacturing discipline.

- Electrical margins shrink first, often before functional failure appears in bring-up testing.

- Manufacturing variation amplifies risk in fine-line HDI structures more than in conventional multilayer boards.

- Cross-sector deployment means the same HDI design may face very different environmental stress profiles.

- Supplier comparison must include process capability, not just nominal electrical targets.

What usually breaks first in high-speed HDI channels?

The earliest breakdown points in signal integrity in HDI design are usually discontinuities, not catastrophic defects. These include abrupt impedance changes at layer transitions, poorly controlled reference plane returns, excessive via stubs, and trace geometries that no longer match the dielectric assumptions used in simulation. In short channels, these issues may look minor. In dense, multi-gigabit systems, they compound quickly.

One frequent mistake is to assume that finer geometry automatically means better performance. HDI enables shorter routes and tighter breakout, but it also increases process sensitivity. Small changes in copper thickness, dielectric spacing, resin flow, and microvia formation can alter impedance enough to affect compliance windows. This is why signal integrity in HDI design must be validated against actual build capability rather than ideal CAD intent.

Primary failure initiators technical evaluators should screen

- Impedance discontinuities at connector launches, BGA escapes, neck-down sections, and layer changes.

- Crosstalk between closely spaced differential pairs or parallel single-ended routes in dense breakout zones.

- Via stubs and unused barrel length that create resonant structures at higher frequencies.

- Reference plane interruptions that force return current detours and increase radiated noise.

- Stack-up mismatch between simulated dielectric constants and actual laminated material behavior.

- Microvia reliability concerns when aggressive density targets push fabrication windows too tightly.

The table below summarizes which mechanisms tend to appear first, how they present in validation, and why they matter in supplier qualification for signal integrity in HDI design.

For procurement and evaluation teams, these patterns help distinguish between a board that merely passes basic continuity tests and one that supports scalable high-speed production. Signal integrity in HDI design is often won or lost at these transition details.

How should technical evaluators compare HDI options across industries?

Not every HDI board serves the same operating envelope. An industrial camera module, an EV control subsystem, a smart agriculture gateway, and a water treatment monitoring unit may all use HDI, yet each prioritizes different trade-offs between speed, thermal cycling, vibration tolerance, and cost. This is where cross-sector benchmarking becomes valuable.

GIM’s multi-disciplinary view is useful because signal integrity in HDI design cannot be evaluated only by nominal bandwidth. The evaluator must consider where the board will operate, what compliance frameworks may apply, and how repeatable fabrication must be across regions or suppliers.

Comparison points that matter more than headline layer count

- Via architecture: stacked, staggered, blind, buried, and back-drilled strategies affect both routing freedom and channel quality.

- Material system: low-loss laminates may improve high-speed performance, but sourcing stability and processing capability must also be checked.

- Process window: fine-line capability on paper does not guarantee repeatable impedance control in production volume.

- Environmental profile: automotive and outdoor infrastructure applications may punish marginal designs more than indoor electronics.

- Validation method: coupon testing, TDR review, insertion loss characterization, and cross-sectional analysis should align with application criticality.

The following comparison table helps technical evaluators align signal integrity in HDI design choices with actual application demands rather than generic board specifications.

This comparison shows why a single “high-performance HDI” label is not enough. Technical evaluators need application-specific thresholds and evidence that the supplier can hold those thresholds in production, not just in prototypes.

What parameters should be checked before supplier approval?

When budgets are tight and delivery schedules are compressed, teams often skip deeper review and approve a source based on stack-up samples or unit price alone. That is risky. Signal integrity in HDI design depends on parameter discipline across design, fabrication, and verification. A capable supplier should be able to discuss these items clearly and consistently.

Pre-approval checklist for technical evaluation

- Target impedance ranges for single-ended and differential traces, plus tolerance limits by layer.

- Actual dielectric thickness capability after lamination, not only nominal pre-layout values.

- Copper roughness and foil type where high-speed loss sensitivity is significant.

- Microvia aspect ratio limits and fill quality expectations for stacked structures.

- Reference plane continuity rules near split regions, connectors, and BGA escapes.

- Testing approach, including coupon strategy, TDR checkpoints, and cross-section sampling.

If the supplier cannot link geometry, materials, and process limits to expected channel behavior, the risk of late-stage redesign rises sharply. In many projects, the first failure is not electrical collapse but expensive uncertainty.

How do standards and compliance affect signal integrity decisions?

Technical evaluators often separate compliance from electrical performance, but in practice they are linked. Signal integrity in HDI design can affect emissions behavior, functional reliability, and traceability expectations. Standards do not replace engineering judgment, yet they provide a common framework for procurement reviews and supplier alignment.

In cross-industry manufacturing, the relevant lens may include IPC guidance for PCB design and fabrication, ISO-based quality frameworks, and IATF-oriented expectations when automotive supply chains are involved. GIM’s value lies in translating these frameworks into benchmark questions: Which process controls support repeatable impedance? Which documentation supports field risk reduction? Which deviations are acceptable for the intended use case?

Useful compliance-oriented questions

- Does the stack-up documentation reflect actual fabrication capability and revision control?

- Are impedance coupons representative of the critical production layers and geometries?

- Is there traceability for material substitutions that could change dielectric performance?

- Are failure analysis paths defined if field returns point to channel instability rather than assembly issues?

These questions reduce the chance of approving a board that looks compliant on paper but performs inconsistently across lots, geographies, or operating conditions.

Common misconceptions that distort HDI selection

Several purchasing and engineering teams still underestimate the hidden cost of poor signal integrity in HDI design. The result is often a false economy: a lower initial board price followed by debug cycles, repeated qualification, EMI investigation, or field instability.

Misconceptions worth challenging

- “If continuity passes, the board is electrically fine.” Continuity says nothing about high-speed margin, reflection behavior, or crosstalk sensitivity.

- “More layers automatically solve routing and integrity problems.” Additional layers help only if reference strategy, via transitions, and dielectric control are also managed well.

- “Simulation guarantees performance.” Simulation is only as good as the material data, via model accuracy, and manufacturing assumptions behind it.

- “One approved supplier profile fits all sectors.” Automotive, industrial, and field-deployed electronics can expose different weaknesses in the same HDI platform.

A disciplined evaluation process should convert these assumptions into testable criteria. That is how teams lower risk without over-specifying every project.

FAQ: what do technical evaluators ask most often?

How do I know whether signal integrity in HDI design is the real problem or just an assembly issue?

Start by separating repeatable channel symptoms from random assembly defects. If failures cluster around higher data rates, temperature shifts, or simultaneous switching conditions, signal integrity is a likely contributor. Review TDR data, insertion loss behavior, reference plane transitions, and via structures before assuming soldering is the root cause.

Which HDI feature creates the earliest high-speed risk?

There is no single answer, but layer transitions and via strategy are frequent early risk points. A clean trace on one layer can still fail as a channel if the transition introduces reflection, stub resonance, or return path disruption. Evaluators should inspect transition design as carefully as line geometry.

What should procurement request from a supplier besides a quote?

Ask for stack-up proposals with tolerances, impedance control methodology, material options, coupon strategy, and known process limits for microvias and fine lines. For critical programs, request clarification on validation flow, expected lead-time impact of material selection, and how engineering changes are documented.

Are low-loss materials always necessary for signal integrity in HDI design?

No. Low-loss materials are important when channel length, frequency content, and margin targets justify them. In some industrial systems, better transition control and cleaner reference design deliver more benefit than switching to a premium laminate. Material selection should follow channel requirements, supply stability, and cost justification.

Why choose us for cross-sector HDI technical evaluation?

GIM helps technical evaluators move from isolated board review to system-aware benchmarking. Our advantage is not limited to electronics. We connect HDI substrate assessment with the broader realities of global manufacturing: supplier consistency, standards alignment, environmental duty cycle, and application-specific risk. That matters when the same sourcing decision influences automotive modules, industrial instrumentation, smart agri-tech devices, or infrastructure monitoring hardware.

If you are reviewing signal integrity in HDI design for qualification, redesign, or supplier comparison, we can support targeted discussions around parameter confirmation, stack-up review, application-fit benchmarking, compliance expectations, delivery-risk screening, and alternative solution paths. Teams also consult GIM for sample evaluation criteria, quote comparison logic, and scenario-based selection guidance when cost, lead time, and reliability must be balanced together.

- Confirm whether your proposed stack-up and via strategy match the required channel margin.

- Compare HDI options by performance risk, manufacturability, and cross-sector compliance exposure.

- Discuss lead-time, material substitution risk, and validation priorities before supplier approval.

- Review sample support, quotation assumptions, and custom benchmarking needs for your program.

When signal integrity in HDI design is treated early as a procurement and engineering decision, failures can be prevented before they become field costs. Contact GIM to discuss stack-up parameters, supplier comparison, certification-related concerns, sample review criteria, or a customized evaluation framework for your next high-density interconnect project.

The Archive Newsletter

Critical industrial intelligence delivered every Tuesday. Peer-reviewed summaries of the week's most impactful logistics and market shifts.